Maixシリーズに搭載されているマイコン「Kendryte K210」の日本語情報です。

目次

おことわり

V0.1.5ベースの情報です。

なるべく原文に忠実な翻訳を心がけていますが、間違いがあればご指摘ください。

データシート原文(英語、中国語)はDownloads – Kendryteから入手できます。

概要

Kendryte K210はマシンビジョンとマシンヒアリングの機能を統合したSystem-On-Chip(SoC)です。

TSMCのUltra-Low-Power(ULP) 28nmプロセス、64bit デュアルコアプロセッサーにより、優れた電力効率、安定性、信頼性を実現しています。

K210は、エッジデバイスに組み込む人工知能をなるべく簡単に、しかも短い期間で開発することを追求したSoCです。

Kendryte K210はAI、IoT端末向けに最適なSoCであり、しかも高性能なMCUでもあります。

Kendryteは中国語のブランド名「勘智」(カンジー)の英訳です。

「勘智」は「勘物探智」に由来する造語です。

Kendryteの主な用途はIoT向け開発であり、すなわち勘物(考え調べること)です。

そしてAIソリューションを提供するので、すなわち探智(知性)です。

- マシンビジョン(Machine Vision)

- マシンヒアリング(Machine Hearing)

- 低消費電力かつ優れた速度と性能の画像処理

- 高性能なハードウェア型CNNアクセラレーター「KPU」

- TSMC 28nmプロセス、動作温度範囲-40〜125℃

- ファームウェア暗号化対応

- 入出力ピンを自在に設定できる独自機能があり、柔軟な設計が可能

- コアの動作電圧が低いため、同等性能のシステムに比べて消費電力が少ない

- 入出力ピンは3.3V/1.8V両対応のためレベルシフトが不要

AIソリューション

マシンビジョン

K210はとても簡単にマシンビジョンソリューションを開発できます。

CNN(畳み込みニューラルネットワーク, Convolutional Neural Network)を少ない消費電力で処理できます。

応用例

- オブジェクト検知(Object Detection)

- 画像分類(Image Classification)

- 顔検知(Detection)と顔認識(Recognition)

- ターゲットのサイズと座標をリアルタイム検知

- 検出したターゲットの種類をリアルタイム検知

マシンヒアリング

K210はマシンヒアリング処理が可能です。

リアルタイムの音源方位推定と指向性処理ができる高性能なアレイマイク用オーディオプロセッサーを搭載しています。

応用例

- 音源方位推定

- 音場(おんば)の可視化(Sound Field Imaging)

- 指向性処理(ビームフォーミング, Beamforming)

- ボイスウェイクアップ(トリガーワードを用いた起動)

- 音声認識(Speech Recognition)

ハイブリッドソリューション

K210は、マシンビジョンとマシンヒアリングの組み合わせにより、さらに強力な機能を実現できます。

音源推定により、画像処理のターゲット追跡をアシストできます。

逆に、画像処理のターゲット情報からマイクの指向性処理のアシストも可能です。

さらに、カメラの映像から人物を検知し、アレイマイクの指向性を人に追従させるアダプティブビームフォーミングも可能です。

同様に、人の声から音源推定して、カメラをしゃべっている人に向けることも可能です。

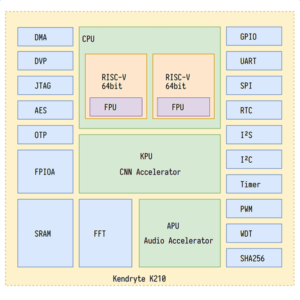

アーキテクチャ概要

K210には2つの64bit RISC-V CPUコアがあり、各コアはFPU(浮動小数点演算ユニット, Floating Point Unit)を内蔵しています。

CNN演算のKPU(Knowledge Processing Unit)とアレイマイク処理のAPU(Audio Processing Unit)は、K210のメイン機能であるマシンビジョンとマシンヒアリングに使われます。

FFT(高速フーリエ変換)のアクセラレーターも搭載しています。

これらのアクセラレーターにより、K210は様々な機械学習アルゴリズムを効率的に処理できます。

AESとSHA256に対応した暗号化アクセラレーターを内蔵し、セキュリティ用途に利用できます。

高性能で低消費電力のSRAMと強力なDMAを搭載しており、高スループットを実現しています。

SRAM……Static RAMの略。リフレッシュ動作が必要なDRAMより低消費電力かつ高速。

DMA……Direct Memory Accessの略。CPUを経由せず、直接、データ転送する方式。

K210は豊富なペリフェラルがあり、様々な用途に対応できます。

DVP, JTAG, OTP, FPIO, GPIO, UART, SPI, RTC, I2S, I2C, WDT, タイマーとPWMを内蔵しています。

端子仕様

K210のピン配置は入念に検証され、信号系端子がBGA外周に配置されています。

PCB基板を設計するときに配線しやすく、電気的特性も安定します。

K210は電圧が異なる複数の電源ドメインがあります。

I/Oは3.3V/1.8V、コアは0.9Vです。

電源ドメインの一覧表はデータシート原文をご確認ください。

ピン配置

K210のピン配置図です。トップビュー(上面図)です。

12×12の144ピン、8x8mm、高さ0.953mmのBGAパッケージです。

端子説明

K210データシート図表をご確認ください。

電源仕様

最大定格は5143mWです。

I/O系が最大3240mW(1.8V供給時)、コアが最大1800mW、その他103mWです。

電圧、消費電流の詳細仕様はデータシート原文をご確認ください。

リセット回路

パワーオン、パワーダウン、電圧低下時に確実にK210をリセットするため、1.8V出力の電源監視ICの使用を推奨します。

特殊ピン

IO_16はBOOTモードの選択に使用します。

パワーオンリセット中、IO_16がHighだとFLASHから起動、LowだとISPモードに入ります。

リセット後、IO_0, IO_1, IO_2, IO_3がJTAGピンです。

IO_4とIO_5はISPピンです。

機能説明

CPU

高性能かつ低消費電力のRISC-V ISAのデュアルコア64bit CPUを搭載しています。

CPUコアの特徴は以下の通りです。

- 2コアで各コアに独立したFPU内蔵

- 高度なアルゴリズムに対応できる64bit CPU

- 動作周波数は400MHz、可変

- 拡張命令セットIMAFDC(RV64GC)ベース

- 倍精度と単精度の浮動小数点演算および積算/除算/平方根演算をサポートするFPU

- プラットフォームレベル割り込みコントローラー(PLIC)

- コアローカル割り込みコントローラー(CLINT)

- 各コアに32KiBのI-Cache(インストラクション・キャッシュ)

- 各コアに32KiBのD-Cache(データ・キャッシュ)

- 合計8MiBのSRAM

命令セット(ISA)

- オープンソースでリソースが充実し、高性能なデュアルコア64bit

- I extension:基本の整数演算

- M extension:整数の乗算、除算。ハードウェアで高速処理。

- A extension:アトミック演算

- C extension:16bit短縮命令(Compressed)

- 安全性を改善するため異なる特権レベルをサポート

FPU

- IEEE754-2008準拠した高性能なパイプラインFPU

- CPUのコア0とコア1にそれぞれ独立したFPUコアを搭載

- F extension:単精度浮動小数点数演算

- D extension:倍精度浮動小数点演算

- ハードウェアによる単精度/倍精度の除算

- ハードウェアによる単精度/倍精度の平方根演算

割り込み制御

RISC-V CPUのPLICは柔軟で高度な割り込み制御が可能です。

7段階の優先順位(priority level)と64個の割り込み源(external interrupt source)を設定可能です。

各コアごとに割り込み制御を個別に設定できます。

- 割り込み管理と割り込み経路はコアごとに個別制御可能

- ソフトウェア割り込みおよびコアをまたぐ割り込みトリガーをサポート

- 各コアで自由に設定できるタイマー割り込み

- 64個の割り込み源それぞれに7段階の優先順位を設定できる高度な割り込み管理

デバッグ

- インストラクションの実行サイクルをカウントするパフォーマンス監視(performance monitor)機能

- ハイスピードUARTとJTAGのインタフェース

- DEBUGモードとハードウェア・ブレークポイント(breakpoint)

KPU(Knowledge Processing Unit)

KPUは畳込み(convolution)、バッチ正規化(batch normalization)、活性化(activation)、プーリング(pooling)の演算機能を内蔵した汎用ニューラルネットワークプロセッサーです。

顔や物体のリアルタイム認識が可能です。

KPUの特徴は以下の通りです。

- 固定小数点モデルをサポート

- ネットワーク層の数に直接的な制約なし。各層のCNNのパラメータは入力/出力のチャンネル数、入力のline width, column heightを含めて個別に設定可能。

- 1×1および3×3の畳み込みカーネルをサポート

- 任意形式の活性化関数をサポート

- リアルタイム処理でサポートされるニューラルネットワークのパラメータサイズは最大5MiB〜5.9MiB

- 非リアルタイム処理の場合、ニューラルネットワークのパラメータサイズはフラッシュメモリーの容量が上限

KPUの内部構造図

※補足1

33ms(30fps)以内のニューラルネットワーク出力が不要な用途、たとえば一般的なオーディオ用途も非リアルタイムのアプリケーションです。

※補足2

K210がサポートするフラッシュメモリーはSPI NOR(8MiB, 16MiB, 32MiB)とSPI NAND(64MiB, 128MiB, 256MiB)です。

APU(Audio Processing Unit)

APUは声の方向と音声データを前処理するモジュール(プリプロセッサー)です。

APUの特徴は以下の通りです。

- 最大8ch(ステレオ4ch)のオーディオ入力

- 最大16方向の指向性処理と前処理を同時に実行可能

- 1つのアクティブな音声ストリームを出力可能

- 音声信号処理精度は16bit

- 入力データは12bit/16bit/24bit/32bitをサポート

- マルチチャンネルの生データを直接出力可能

- 最大サンプリングレートは192kHz

- 512ポイントのFFT機能

- DMAコントローラー対応

SRAM

K210のSRAMは汎用メモリ(6MiB)とAI用メモリ(2MiB)の計8MiBに分割されています。

AI用メモリはKPU用に割り当てられたメモリです。

SRAMは連続したアドレスに配置されており、CPUのキャッシュインタフェースからも、キャッシュされていないインタフェースからも直接アクセスできます。

アドレスマップはデータシート原文をご確認ください。

汎用SRAM

汎用SRAMはマイコン通常動作時は常にアクセス可能です。

MEM0とMEM1の2つのバンクに分割されており、DMAコントローラーは両方のバンクで同時に動作できます。

AI用SRAM

AI用SRAMは下記条件をすべて満たすときだけアクセス可能です。

・PLL1が有効かつクロックが適切に設定されている

・KPUがニューラルネットワークの計算を実行していない

システムコントローラー(SYSCTL)

下記のシステム制御レジスタを含めて、K210のクロックとリセットを制御します。

・PLLの周波数

・クロックの選択

・ペリフェラルのクロック分周比

・クロックの有効化

・モジュールのリセット

・DMAのハンドシェイク信号の選択

FPIO(Field Programmable IO Array, IOMUX)

255個の内部機能を48個の入出力ピンに自由に割り当て可能です。

- プログラマブルなIO機能

- 出力ピンの電流駆動能力(drive strength)は8種類のオプション

- プルアップ/プルダウンを内部レジスタで選択可能

- シュミットトリガの入力オプション

- 出力スルーレートの設定

- 内部入力レベルの設定

ワンタイムメモリ(OTP)

OPT(One-Time Programmable Memory)の特徴は以下の通りです。

- 大容量128Kbit

- 内部で複数のブロックに分割されており、各ブロックに書き込み保護(write protection bit)を設定可能

- メモリー修復(dead bit repair)

- 一部のSoCのハードウェア回路の動作を制御する64個のフラグ(REGISTER_ENABLE)

- ハードウェア書き込み専用の信頼性が高い記憶領域として128bit AES暗号化/復号化の鍵を保存可能

AESアクセラレーター

暗号化と復号化を行うアクセラレーターです。

AESアクセラレーターの特徴は以下の通りです。

- 暗号化モード:ECB/CBC/GCM

- 鍵長:128bit/192bit/256bit

- 鍵はソフトウェアで生成可能かつハードウェア回路で保護可能

- DMA転送対応

DVP(Digital Video Port)

DVPはカメラ用インタフェースのモジュールで、特徴は以下の通りです。

- DVPインタフェースのカメラに対応

- SCCBプロトコルによるカメラ設定

- 最大フレームサイズ:640×480ピクセル

- 入力フォーマット:YUV422/RGB565

- KPUとディスプレイに同時出力可能

- KPUへの出力フォーマット:RGB888, YUV422入力時のY信号

- ディスプレイへの出力フォーマット:RGB565

- フレーム開始時と転送終了時に割り込み信号をCPUに送信可能

FFTアクセラレーター

FFT機能をハードウェアで実装しています。

- ポイント数:64/128/512

- FFTおよびIFFT

- 入力:32bit/64bit

- 実数および複素数を入力可能

- DMA転送対応

SHA256アクセラレーター

SHA-256計算用のアクセラレーターです。

- SHA-256計算

- 入力データのDMA転送対応

UART(Universal Asynchronous Transceiver)

ハイスピードUART

High speed UART UARTHS(UART0)

- ボーレート最大5Mbps

- 送信および受信のFIFOサイズは8byte

- プログラマブルなTHRE割り込み

- ハードウェアのフロー制御、その他のモデム制御信号や同期式シリアル転送プロトコルは非対応

汎用UART

UART1, UART2, UART3は汎用UARTです。

・非同期通信(RS232,RS485,IRDA)

・ボーレート最大5Mbps

・CTS/RTSを使ったハードウェア・フロー制御

・XON/XOFFを使ったソフトウェア・フロー制御

・DMA転送対応

- 送信および受信のFIFOサイズは8byte

- 非同期クロック対応

- データ同期のためのCPUのボーレート要件に対応するため、UARTでは送信と受信のデータクロックを別々に設定できます。全二重モードでは2つのクロックドメインのデータ同期を確実に行うことができます。

- RS485インタフェース対応

- デフォルトはRS232モードです。ソフトウェアでRS485モードに設定できます

- プログラマブルなTHRE割り込み

- THRE割り込みモードでシリアルポートのパフォーマンスを向上できます。THREモードとFIFOモードを選択すると、FIFOサイズが閾値以下になるとTHRE割り込みが発生します。

ウォッチドッグタイマー(WDT)

WDTはAPBのスレーブペリフェラルで、”common hardware component design”の一部です。

K210はWDT0とWDT1という2つのウォッチドッグタイマーがあります。

WDTは以下のモジュールを内蔵しています。

- APBスレーブインタフェース

- 現在のカウンタ値と同期するレジスタ

- 割り込みとシステムリセットのモジュール、ダウンカウンタ付ロジック制御回路

- 非同期クロックと同期するための同期クロックドメイン

WDTは以下の設定に対応します。

- APBバス幅:8bit/16bit/32bit

- タイムアウト処理のためクロックカウンタは設定値から0に向けてカウントダウン

- カウントレートを制御するため、オプションで外部クロックを選択可能

- タイムアウト発生時、WDTは以下のタスクを実行可能

- システムリセット信号を生成

- 割り込みサービスでビットがクリアされていても、最初に割り込みを発生させ、その後にシステムリセット信号を生成

- デューティサイクルを設定可能

- プログラマブルまたはハードウェア設定のカウンタ開始値

- カウンタリセット保護

- ポーズモード(外部ポーズ信号が有効な場合)

- WDTの意図しない無効化保護

- カウンタ機能のテストモード(デクリメント動作)

- 外部の非同期クロックに対応。この機能を有効にするとAPBバスクロックがOFFであってもクロック割り込みとシステムリセット信号が発生。

汎用入出力インタフェース(GPIO)

ハイスピードGPIO

K210には32個のハイスピードGPIO(GPIOHS)があります。

ハイスピードGPIOの特徴は以下の通りです。

- 入力か出力を選択可能

- 各IOを独立した割り込み源として設定可能

- エッジトリガまたはレベルトリガとしての割り込み

- 各IOは48ピンあるFPIOAのひとつとして割り当て可能

- プルアップ/プルダウン/ハイインピーダンスを選択可能

DMAC(Direct Memory Access Controller)

DMACは柔軟な構成が可能でバスのデータ転送効率に優れています。

マルチマスターとマルチチャンネルをサポートしています。

DMACの機能は以下の通りです。

- メモリ-メモリ間、メモリ-ペリフェラル間、ペリフェラル-メモリ間、ペリフェラル-ペリフェラル間でデータ転送可能

- コアクロックとスレーブクロックが独立している

- すべてのペリフェラルが非アクティブの場合、メインインターフェースはクロックをオフにして消費電力を削減できる

- 最大8チャンネル、それぞれが独自のソースとデスティネーションのペアを持てる

- 各チャンネルのデータをいちど転送できるのは一方向のみ

- 入力ピンはデスティネーションサイズを動的に選択可能

- チャンネル・ロック対応

- 内部チャンネルのバス・アービトレーション機能。データ転送の優先度に基づいてメイン・インタフェース・バスの特権レベルを設定

- DMACステータス出力、アイドル/ビジー表示

- 各DMAの転送中断、転送完了などのステータス

I2C(Inter-Integrated Circuit Bus)

3つのI2Cバス・インタフェースがあり、マスターかスレーブか選択可能です。

- 標準モード(0~100Kb/s)

- 高速モード(最大400Kb/s)

- 7bit/10bit アドレッシングモード

- バルク転送モード

- 割り込みまたはポーリングモード動作

SPI(Serial Peripheral Interface)

4つのSPIインターフェースがあります。

SPI0、SPI1、SPI3はマスターモード専用です。

SPI2はスレーブモード専用です。

- 1/2/4/8線式の全二重モード対応

- SPI0、SPI1、SPI2のクロックは最大25MHz(確認中)

- SPI3のクロックは最大100MHz(確認中)

- 32bit x 32byteのFIFO

- 独立してマスクされた割り込み:ホスト競合、送信FIFOオーバーフロー、送信FIFOエンプティ(empty)、受信FIFOフル(full)、受信FIFOアンダーフロー、受信FIFOオーバーフロー

- DMA転送対応

- デュアルエッジDDR伝送モード対応

- SPI3はXIP対応

I2S(Inter-Integrated Sound)

3つのI2Sインタフェース(I2S0、I2S1、I2S20)があり、マスターモード専用です。

I2S0はAPU(音声処理ブロック)に接続してボイス・エンハンスメント(指向性処理)と音源方向推定を利用可能です。

すべてのI2Sインターフェイスは以下の機能をサポートしています。

- バス幅:8bit/16bit/32bit

- インターフェイスごとに最大4つのステレオチャンネル

- 全二重通信、送信と受信の独立動作

- APBバス・クロックとI2S SCLKは非同期

- オーディオデータ分解能:12bit/16bit/20bit/24bit/32bit

- I2S0は送信FIFO:64byte、受信FIFO:8byte

- I2S1とI2S20のFIFOは送信、受信ともに8byte

- DMA転送対応

- プログラマブルなFIFOしきい値

タイマー

3つのタイマーモジュールがあり、仕様は以下の通りです。

- カウンタ幅:32bit

- カウントアップ、カウントダウンを選択可能

- 独立したクロック

- 割り込みごとに極性を設定可能

- 個別または組み合わせの割り込み出力フラグとして設定可能

- 各タイマーは読み書き一貫性のあるレジスタを保有

- タイマーリロード出力(タイマーカウンタがリロードされるたびに切り替わる)

- 出力PWMモード(デューティ比:0%-100%)

ROM(Read Only Memory)

AXI ROMはユーザのアプリケーションプログラムをSPI FlashやSRAMからコピーする役割です。

- AES-128-CBCのファームウェア復号化に対応

- FlashをプログラムするためのUOPモード

- 耐タンパー性。SHA256ファームウェアの整合性(integrity)チェック。

- UOPモード、SHA256チェック、AES復号化を無効にするためにOTPを設定可能

- 起動時にK210を高い周波数で動作させるTURBOモードへの移行に対応

リアルタイムクロック(RTC)

RTCはリアルタイムを保持するモジュールで、特徴は以下の通りです。

- 外部リファレンス(水晶振動子)に対応

- 外部水晶振動子の周波数と分周比を設定可能

- 年月日、時分、週を含む永久カレンダー

- 秒単位でカウントし、現在の時刻を参照可能

- アラーム設定。年月日、時、分、秒を指定し、期日になると割り込みトリガーが発生。

- 周期的なタイマー設定。設定した日、時、分、秒単位で割り込みトリガーが発生。

- 読み出しカウンタの分解能は1秒未満、分解能は外部の水晶振動子の1周期

- 電源投入/リセット後はデータ消去される

PWM(Pulse Width Modulation)

PWMモジュールはパルス出力のデューティ比の制御に使います。

以下の機能を設定できます。

- 周波数または周期を指定

- PWMタイマーは他のPWMタイマーやモジュールと同期可能

- PWMタイマーは他のPWMタイマーやモジュールと位相をそろえることが可能

- タイマーカウントモード:カウントアップ、カウントダウン、アップとダウンのループ

- プリスケーラを使用してPWMタイマークロック(PT_clk)のレートを変更可能。各タイマーは独自のプリスケーラがあり、PWM_TIMER0_CFG0_REGレジスタのPWM_TIMERx_PRESCALEで設定可能。PWMタイマーのカウントは設定された低速なレートになる。

電気的特性

電源電圧や消費電流の仕様が規定されています。

また、出力ピンの電流駆動能力の設定値がLow/High、それぞれ記載されています。

数値が主なので省略します。

パッケージ情報

BGA-144パッケージです。

電気的特性と熱抵抗に優れるフリップチップ技術を採用しています。

寸法図はデータシート原文をご確認ください。

KPUは

Knowledge Processing Unit

の略だそうですよ〜

ご指摘ありがとうございます。修正反映しました。KPUはデータシート原文では(Neural Network Processor) と説明があり、なにの略語なのか、あいまいでした。Kernel Processing Unitだと類推していましたが、たしかに調べてみると、Sipeedブログ等でもKnowledge Processing Unitと説明されていました。